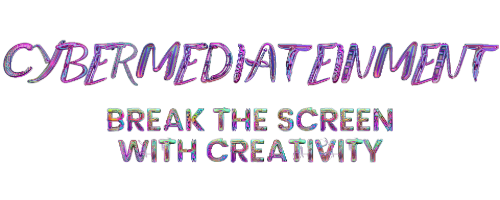

La Rivoluzione delle Architetture Logiche

Come siamo passati da una CPU universale a processori specializzati — e perché questa frattura è potere

CPU: Settant’anni di stabilità, dieci anni di rivoluzione

Dal 1945 al 2005, il computing è stato dominato da un’unica architettura fondamentale: la CPU (Central Processing Unit) basata sul modello stored-program. Per sessant’anni, ogni miglioramento è arrivato facendo la stessa cosa meglio e più velocemente: più transistor, frequenze più alte, cache più grandi. Questo modello ha funzionato. Ha colonizzato il mondo.

Poi, tra il 2005 e il 2015, è successo qualcosa di irreversibile: l’emergere di architetture radicalmente diverse. GPU che processano migliaia di operazioni in parallelo. TPU progettate per moltiplicazioni matriciali. NPU ottimizzate per inferenza edge. LPU che eliminano il non-determinismo per velocità estrema.

Questa non è una storia di progresso lineare. È una storia di crisi: quando le vecchie soluzioni smettono di funzionare, il sistema si reinventa — e nella reinvenzione si concentra potere.

L’era della CPU universale (1945–2005)

Gli inventori dimenticati delle CPU: Eckert e Mauchly

La storia inizia nel 1945, alla Moore School of Electrical Engineering dell’Università della Pennsylvania. J. Presper Eckert e John Mauchly avevano appena completato l’ENIAC: il primo computer digitale elettronico su scala reale, grande come una stanza.

La loro idea rivoluzionaria: invece di “programmare” la macchina riconfigurando cavi, perché non memorizzare i programmi nella stessa memoria dei dati? Il concetto stored-program è il fondamento del computing moderno. John von Neumann documentò queste idee nel “First Draft of a Report on the EDVAC” (1945): il documento circolò, e l’architettura divenne “von Neumann”. Un classico: lavoro collettivo attribuito a chi ha più prestigio.

L’architettura: potenza e limite delle CPU tradizionali

- Memoria unificata: programmi e dati nello stesso spazio

- Unità di controllo: coordina l’esecuzione

- ALU: esegue operazioni aritmetico-logiche

- Input/Output: interfaccia con il mondo esterno

La separazione tra processore e memoria, connessi da un bus, è geniale e disastrosa allo stesso tempo: flessibilità totale, ma anche dipendenza dal movimento dei dati. È qui che nasce il bottleneck.

Il bottleneck: il prezzo della generalità

Nel 1977, John Backus (Turing Award) lo dice chiaramente: il problema non è calcolare, è spostare. Il calcolo è velocissimo; l’attesa della memoria è la tassa strutturale dell’architettura universale.

Le “leggi magiche” delle CPU: Moore e Dennard (1965–2005)

Per quarant’anni, l’industria ha evitato il collasso con lo scaling tecnologico: Legge di Moore (più transistor) e Dennard Scaling (più piccoli = meno potenza). È stato il “free lunch” del computing: bastava aspettare.

Intel 4004 (1971): 2.300 transistor, 740 KHz · Pentium (1993): 3,1 milioni, 60 MHz · Pentium 4 (2000): 42 milioni, 1,5 GHz

2005: la crisi — la “Heat Wall” delle CPU

Intorno al 2005, le frequenze si fermano. Non per mancanza di idee, ma per fisica. Il Dennard Scaling collassa: aumentare clock significa surriscaldamento. È la power wall. Il modello della CPU universale raggiunge un limite non negoziabile.

La soluzione temporanea: CPU multi-core (2005–2010)

Se non possiamo rendere un core più veloce, mettiamo più core. Ma il parallelismo non è gratis: il software deve essere riscritto, e la Legge di Amdahl mette un limite teorico all’accelerazione. E mentre aumentano i transistor, compare il dark silicon: porzioni del chip che devono restare spente per vincoli termici.

La scoperta del parallelismo — l’era GPU (2006–2012)

2006: NVIDIA cambia il gioco

NVIDIA fa una mossa strategica: trasforma un processore grafico in motore di computing parallelo. Le GPU sono architetturalmente opposte alle CPU: meno controllo sofisticato, più throughput massivo. Pochi core “intelligenti” contro migliaia di core “semplici”.

Il momento “Aha”: moltiplicazione matriciale

Grafica 3D e deep learning condividono lo stesso cuore: moltiplicazioni matriciali massive. Quando la comunità dimostra che le GPU accelerano l’addestramento, il punto non è “più veloce”: è “improvvisamente possibile”.

CUDA: l’ecosistema che crea un monopolio

La mossa decisiva si chiama CUDA (2006): programmare GPU diventa accessibile, ma con una condizione: l’ecosistema è proprietario e funziona solo su NVIDIA. È qui che il vantaggio tecnico si trasforma in rendita strutturale.

2012: AlexNet — l’esplosione

AlexNet vince ImageNet e inaugura l’era del deep learning pratico. Il training su GPU diventa standard. Ma ciò che si consolida non è solo una tecnologia: è una dipendenza industriale dall’interfaccia software.

Google e la crisi dell’inferenza — l’era TPU (2013–2024)

2013: il calcolo che spaventa Google

Se ogni servizio di scala planetaria integra reti neurali, i datacenter esplodono. Le GPU sono ottime per training, ma l’inferenza (milioni di richieste, una alla volta) è un altro regime: latenza, efficienza, costo operativo.

TPU v1: specializzazione assoluta

Google costruisce un ASIC dedicato: la TPU. Architettura chiave: systolic array. L’idea è brutale: riuso dei dati, minimizzazione degli accessi alla memoria durante il calcolo. È la risposta diretta al vero nemico: la memoria, non l’ALU.

l’ecosistema batte la performance

Anche quando l’hardware è competitivo o superiore, l’adozione dipende dall’ecosistema. CUDA domina la formazione, i framework, le librerie, il mercato del lavoro. Il controllo dello strato software decide più dell’hardware.

AI al confine delle CPU — l’era NPU (2014–presente)

Training nel cloud, inferenza ovunque

L’AI deve vivere su smartphone, laptop, IoT, auto. Una GPU discreta consuma troppo. La risposta è la NPU: accelerazione integrata, low power, low precision, inferenza real-time. L’AI diventa ubiqua — e invisibile.

Capitolo 5: Il problema sequenziale — l’era LPU (2024–presente)

LLM: un token alla volta

I Large Language Models generano testo in modo autoregressivo: token n+1 dipende da token n. È un workload strutturalmente sequenziale. Su GPU, l’inferenza diventa memory-bound: l’hardware aspetta i dati più di quanto calcoli.

LPU: determinismo come arma

L’idea LPU: togliere “intelligenza” all’hardware e mettere controllo nel compilatore. Scheduling statico, riduzione del non-determinismo, minimizzazione degli accessi memoria. È specializzazione estrema: efficienza e latenza, in cambio di flessibilità.

Cinque architetture, una divisione del lavoro

| Architettura | Ottimizzata per | Punti forza | Leader | Dove |

|---|---|---|---|---|

| CPU | Control flow, carichi irregolari | Flessibilità, low-latency | Intel, AMD, ARM | Ovunque |

| GPU | Training AI, parallelismo massiccio | Throughput, ecosistema maturo | NVIDIA | Datacenter, workstation |

| TPU | Training large-scale, inferenza batch | Efficienza, integrazione stack | Cloud/servizi interni | |

| NPU | Inferenza edge, mobile AI | Potenza ridotta, on-device | Apple, Qualcomm, Samsung | Smartphone, laptop, IoT |

| LPU | Inferenza LLM real-time | Determinismo, bassa latenza | Groq (ecosistemi dedicati) | Servizi di inferenza |

Architetture logiche: specializzazione = efficienza, ma anche concentrazione

Ogni transizione risolve un bottleneck specifico. Ma ogni soluzione, quasi sempre, sposta potere: verso chi controlla l’interfaccia (software), la produzione (fonderie), e l’ecosistema (formazione + librerie + toolchain). La specializzazione non è solo ingegneria. È politica industriale.

CUDA come rendita tecnologica

L’egemonia non si misura solo in TFLOPS. Si misura in costi di migrazione, in dipendenze, in lock-in. Quando una piattaforma diventa “l’università”, “lo standard” e “il mercato del lavoro”, l’hardware è solo la faccia visibile del potere.

Il chokepoint produttivo

I chip avanzati richiedono nodi produttivi e macchine che esistono in pochissimi luoghi. L’infrastruttura computazionale diventa un single point of failure geopolitico. Non è un dettaglio: è una condizione strutturale del futuro digitale.

Conclusioni: verso quale futuro?

In settant’anni siamo passati da una CPU universale a un ecosistema fratturato di acceleratori. Ogni frattura aumenta efficienza, ma riduce controllo distribuito. La conoscenza è prodotta collettivamente; il controllo tende a concentrarsi privatamente.

Fonti CPU

Link in apertura su nuova pagina.

- Gordon E. Moore (1965) — “Cramming more components onto integrated circuits”

- Robert H. Dennard et al. (1974) — “Design of ion-implanted MOSFET’s with very small physical dimensions”

- John Backus (1978) — “Can Programming Be Liberated from the von Neumann Style?”

- Raina, Madhavan, Ng (2009) — GPU per deep learning (NIPS/NeurIPS)

- Krizhevsky, Sutskever, Hinton (2012) — “ImageNet Classification with Deep Convolutional Neural Networks”

- Jouppi et al. (2017) — “In-Datacenter Performance Analysis of a Tensor Processing Unit”

- Kung & Leiserson (1978) — Systolic arrays (paper storico sul paradigma)